- PCI Express (8-lane) interface

- 2 channels sampled at 16-bit resolution

- 250 MS/s real-time sampling rate

- 2 Gigasample dual-port memory buffer

- Continuous streaming mode

- DC-coupled inputs

- Asynchronous DMA device driver

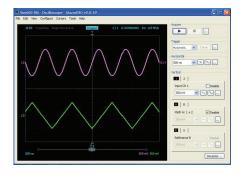

- AlazarDSO® oscilloscope software

- Software Development Kit supports C/C++, C#, Python, MATLAB<sup>®</sup>, LabVIEW<sup>®</sup>

- Support for Windows<sup>®</sup> & Linux<sup>®</sup>

| Product | Bus     | Operating<br>System                        | Channels | Sampling<br>Rate       | Bandwidth  | Memory Per<br>Channel  | Resolution |

|---------|---------|--------------------------------------------|----------|------------------------|------------|------------------------|------------|

| ATS9626 | PCIe x8 | 32-bit/64-bit<br>Windows &<br>64-bit Linux | 2        | 250 MS/s<br>to 50 MS/s | DC-120 MHz | Up to<br>2 Gigasamples | 16 bits    |

#### **Overview**

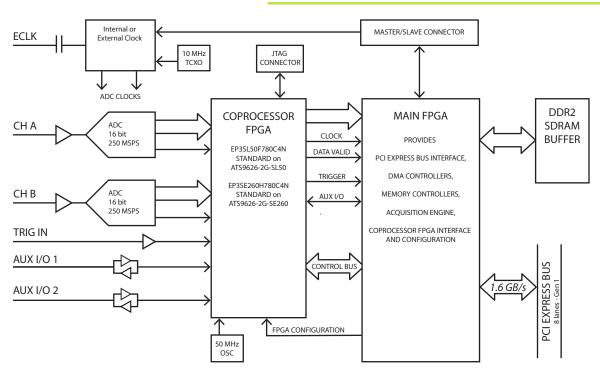

AlazarTech ATS\*9626 is an 8-lane PCI Express (PCIe x8), dual-channel, high speed, 16 bit, 250 MS/s waveform digitizer card with dc-coupled inputs capable of streaming acquired data to PC memory at rates up to 1.6 GB/s or storing it in its deep on-board dual-port acquisition memory buffer of up to 2 Gigasamples.

The on-board Coprocessor FPGA is an Altera Stratix III device with on-chip memory, hardware multipliers, DSP blocks and a fast fabric that allows both integer based and floating point digital signal processing.

All data acquired by the on-board A/D converters flows through the Coprocessor FPGA.

The main difference between ATS9626 and ATS9625 is input coupling: ATS9626 provides dc coupling, whereas ATS9625 provides ac coupling.

ATS9626 is supplied with AlazarDSO software that lets the user get started immediately without having to go through a software development process.

Users who need to integrate the ATS9626 in their own program can purchase a software development kit, ATS-SDK, for C/C++, C#, Python, MATLAB and LabVIEW for both Windows and Linux operating systems.

All of this advanced functionality is packaged in a low power, half-length PCI Express card.

#### **Applications**

Optical Coherence Tomography (OCT)

Radar/RF Signal Recording & Analysis

Ultrasonic & Eddy Current NDT/NDE

Terabyte Storage Oscilloscope

High Resolution Oscilloscope

Lidar

Spectroscopy

Digital Down Conversion (DDC)

Multi-Channel Transient Recording

**Please note:** It is no longer possible for users to design their own Coprocessor FPGA.

We have discontinued the ATS962x Coprocessor FPGA Development Kit (also called ATS9626-FDK) due to lack of demand.

# AlazarTech

## ATS9626 250 MS/s I6-Bit DC-coupled PCIe Digitizer

### **PCI Express Bus Interface**

ATS9626 interfaces to the host computer using an 8-lane PCI Express bus. Each lane operates at 2.5 Gbps.

According to PCIe specification, an 8-lane board can be plugged into any 8-lane or 16-lane slot, but not into a 4-lane or 1-lane slot. As such, ATS9626 requires at least one free 8-lane or 16-lane slot on the motherboard.

The physical and logical PCIe x8 interface is provided by an on-board FPGA, which also integrates acquisition control functions, memory management functions and interface to Coprocessor FPGA. This very high degree of integration maximizes product reliability.

The AlazarTech® bus benchmark has been proven on many computers, including workstation and server class machines from Dell and HP, as well as no-name machines built around motherboards from Intel, ASUS, Tyan, Supermicro etc.

Users must always be wary of throughput specifications from manufacturers of waveform digitizers. Some unscrupulous manufacturers tend to specify the raw, burst-mode throughput of the bus. Others mention data throughput rates to operating system kernel memory, not user accessible memory.

AlazarTech, on the other hand, specifies the benchmarked sustained throughput to buffers in user space.

To achieve such high throughput, a great deal of proprietary memory management logic and kernel mode drivers have been designed by AlazarTech.

#### **Analog Input**

ATS9626 has two dc-coupled analog input channels. Each channel has analog input bandwidth from DC to 120 MHz.

The full scale input range is fixed at  $\pm 1.25$  V.

For applications that require capture of small signals, customers can purchase the ATS9626-014 upgrade that allows the input range to be permanently changed to  $\pm 200$  mV. It should be noted that the analog input bandwidth is limited to 100 MHz with this upgrade.

Input impedance of both channels is fixed at 50  $\Omega$ .

#### **Acquisition System**

ATS9626 PCI Express digitizers use state of the art 250 MSPS, 16-bit ADCs to digitize the input signals. The real-time sampling rate of the ADCs ranges from 250 MS/s down to 50 MS/s.

The two channels are guaranteed to be simultaneous, with a maximum clock skew of 10 ps. Additive jitter of the clock distributor circuit is less than 225 fs<sub>rms</sub>.

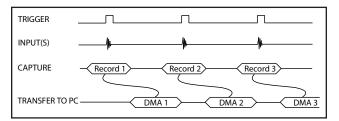

An acquisition can consist of multiple records, with each record being captured as a result of one trigger event. A record can contain both pre-trigger and post-trigger data.

Infinite number of triggers can be captured by ATS9626, when it is operating using dual-port memory.

In between the multiple triggers being captured, the acquisition system is re-armed by the hardware within 256 sampling clock cycles.

This mode of capture, sometimes referred to as Multiple Record, is very useful for capturing data in applications with a very rapid or unpredictable trigger rate. Examples of such applications include medical imaging, ultrasonic testing, OCT and NMR spectroscopy.

#### **Coprocessor FPGA**

ADC data flows through the Coprocessor FPGA before it is stored in the on-board memory or transferred to host PC memory.

Note: it is no longer possible for users to design their own Coprocessor FPGA. The ATS962x Coprocessor FPGA Development Kit has been discontinued.

#### **High-Capacity Coprocessor FPGA**

The ATS9626-2G-SL50 digitizer includes an Altera Stratix III EP3SL50F780C4N device for the Coprocessor FPGA. For some users, this FPGA may not have enough resources to implement their entire design.

In such situations, users can order ATS9626-2G-SE260 to have the high-capacity EP3SE260H780C4N Coprocessor FPGA.

Note that orders for high capacity FPGA may have a significant lead-time.

#### **On-Board Acquisition Memory**

ATS9626 supports on-board memory buffers of 2 Gigasamples.

Acquisition memory can either be divided equally between the two input channels or devoted entirely to one of the channels.

The main advantage of having on-board memory is that it acts as a very deep FIFO between the Analog to Digital converters and PCI Express bus, allowing very fast sustained data transfers across the bus, even if the operating system or another motherboard resource temporarily interrupts DMA transfers.

#### **Maximum Sustained Transfer Rate**

PCI Express support on different motherboards is not always the same, resulting in significantly different sustained data transfer rates. The reasons behind these differences are complex and varied and will not be discussed here.

ATS9626 users can quickly determine the maximum sustained transfer rate for their motherboard by inserting their card in a PCIe slot and running the Tools:Benchmark:Bus tool provided in AlazarDSO software.

ATS9626, which is equipped with dual-port on-board memory, will be able to achieve this maximum sustained transfer rate.

#### **Recommended Motherboards or PCs**

Many different types of motherboards and PCs have been benchmarked by AlazarTech. The ones

that have produced the best throughput results (as high as 1.7 GB/s for PCIe Gen1) are listed here: www.alazartech.com/images-media/2246-AlazarTech RecommendedMotherboards.pdf.

It should be noted that some motherboards may behave unexpectedly. For example, one customer purchased a P6T6 motherboard (instead of P6T7) and found that the throughput was limited to approximately 800 MB/s because P6T6 only supports 4-lane PCI Express connection, even though it uses the same x58 chipset.

#### **Traditional AutoDMA**

In order to acquire both pre-trigger and post-trigger data in a dual-ported memory environment, users can use Traditional AutoDMA.

Data is returned to the user in buffers, where each buffer can contain from 1 to 8191 records (triggers). This number is called RecordsPerBuffer.

Users can also specify that each record should come with its own header that contains a 40-bit trigger timestamp.

A BUFFER\_OVERFLOW flag is asserted if more than 512 buffers have been acquired by the acquisition system, but not transferred to host PC memory by the AutoDMA engine.

In other words, a BUFFER\_OVERFLOW can occur if more than 512 triggers occur in very rapid succession, even if all the on-board memory has not been used up.

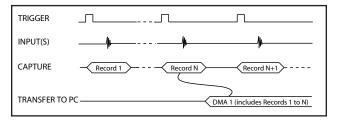

#### No Pre-Trigger (NPT) AutoDMA

Many ultrasonic scanning and medical imaging applications do not need any pre-trigger data: only post-trigger data is sufficient.

NPT AutoDMA is designed specifically for these applications. By only storing post-trigger data, the memory bandwidth is optimized and the entire onboard memory acts like a very deep FIFO.

Note that a DMA is not started until RecordsPerBuffer number of records (triggers) have been acquired and

written to the on-board memory.

NPT AutoDMA buffers do not include headers. However, users can specify that each record should come with its own footer that contains a 40-bit trigger timestamp. The footer is called NPT Footer.

More importantly, a BUFFER\_OVERFLOW flag is asserted only if the entire on-board memory is used up. This provides a very substantial improvement over Traditional AutoDMA.

NPT AutoDMA can easily acquire data to PC host memory at the maximum sustained transfer rate of the motherboard without causing an overflow.

This is the recommended mode of operation for most ultrasonic scanning, OCT and medical imaging applications.

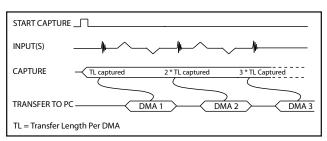

#### **Continuous AutoDMA**

Continuous AutoDMA is also known as the data streaming mode.

In this mode, data starts streaming across the PCI Express bus as soon as the ATS9626 is armed for acquisition. It is important to note that triggering is disabled in this mode.

Continuous AutoDMA buffers do not include headers, so it is not possible to get trigger time-stamps.

A BUFFER\_OVERFLOW flag is asserted only if the entire on-board memory is used up.

The amount of data to be captured is controlled by counting the number of buffers acquired. Acquisition is stopped by an AbortCapture command.

Continuous AutoDMA can easily acquire data to PC host memory at the maximum sustained transfer rate of the motherboard without causing an overflow. This is the recommended mode for very long signal recording.

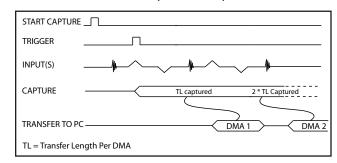

#### **Triggered Streaming AutoDMA**

Triggered Streaming AutoDMA is virtually the same as Continuous mode, except the data transfer across the bus is held off until a trigger event has been detected.

Triggered Streaming AutoDMA buffers do not include headers, so it is not possible to get trigger time-stamps.

A BUFFER\_OVERFLOW flag is asserted only if the entire on-board memory is used up.

As in Continuous mode, the amount of data to be captured is controlled by counting the number of buffers acquired.

Acquisition is stopped by an AbortCapture command.

Triggered Streaming AutoDMA can easily acquire data to PC host memory at the maximum sustained transfer rate of the motherboard without causing an overflow.

This is the recommended mode for RF signal recording that has to be started at a specific time, e.g. based on a GPS pulse.

#### **Master/Slave Systems**

Users can create a multi-board Master/Slave system by synchronizing up to four ATS9626 boards using an appropriate SyncBoard-9626.

SyncBoard-9626 is a mezzanine board that connects to the Master/Slave connector along the top edge of the ATS9626 and sits parallel to the motherboard. For additional robustness, users can secure the SyncBoard-9626 to a bracket mounted on each of the ATS9626 boards.

SyncBoard-9626 is available is available in different widths: 2x, 4x, 2x-W, 3x-W or 4x-W.

SyncBoards with the -W suffix provide 2-slot spacing between ATS9626 cards to support some of the newer motherboards that space out the on-

board x8 or x16 slots by two slots. The -W SyncBoards are also a better solution from thermal point of view, as there is better air flow with 2-slot spacing.

The 2x and 2x-W models allows a 2-board Master/Slave system; the 3x-W model allows a 2 or 3-slot Master/Slave system; and the 4x and 4x-W models allow 2, 3 or 4 board Master/Slave systems.

The Master board's clock and trigger signals are copied by the SyncBoard-9626 and supplied to all the Slave boards. This guarantees complete synchronization between the Master board and all Slave boards.

It should be noted that SyncBoard-9626 does not use a PLL-based clock buffer, allowing the use of variable frequency clocks in Master/Slave configuration.

A Master/Slave system samples all inputs simultaneously and also triggers simultaneously on the same clock edge.

#### **Asynchronous DMA Driver**

The various AutoDMA schemes discussed above provide hardware support for optimal data transfer. However, a corresponding high performance software mechanism is also required to make sure sustained data transfer can be achieved.

This proprietary software mechanism is called Async DMA (short for Asynchronous DMA).

A number of data buffers are posted by the application software. Once a data buffer is filled, i.e. a DMA has been completed, ATS9626 hardware generates an interrupt, causing an event message to be sent to the application so it can start consuming data. Once the data has been consumed, the application can post the data buffer back on the queue. This can go on indefinitely.

One of the great advantages of Async DMA is that almost 95% of CPU cycles are available for data processing, as all DMA arming is done on an event-driven basis.

To the best of our knowledge, no other supplier of waveform digitizers provides asynchronous software drivers. Their synchronous drivers force the CPU to manage data acquisition, thereby slowing down the overall data acquisition process.

#### **Triggering**

ATS9626 is equipped with sophisticated digital triggering options, such as programmable trigger thresholds and slope on any of the input channels or the External Trigger input.

Coprocessor FPGA has access to external trigger and two auxiliary I/O signals.

While most oscilloscopes offer only one trigger engine, ATS9626 offers two trigger engines (called Engines J and K).

The user can specify the number of records to capture in an acquisition, the length of each record and the amount of pre-trigger data.

A programmable trigger delay can also be set by the user. This is very useful for capturing the signal of interest in a pulse-echo application, such as ultrasound, radar, lidar etc.

#### **External Trigger Input**

The external trigger input on the ATS9626 is labeled TRIG IN on the face plate.

External Trigger must an LVTTL digital signal, i.e. 0 to

3.3 V TTL signal. Minimum pulse height requirement is 2.0 Volts. Input impedance of this input is 6.4  $k\Omega$ .

Analog signals and smaller amplitude digital signals will not be detected as trigger events.

User can select between rising edge and falling edge of this signal as the trigger event.

It should be noted that the TRIG IN signal passes through the Coprocessor FPGA. This description of TRIG IN applies to the default Coprocessor FPGA shipped with ATS9626 drivers. A custom Coprocessor FPGA can completely change the functionality of this signal.

#### **Timebase**

ATS9626 timebase can be controlled either by onboard low-jitter VCO or by optional External Clock.

On-board low-jitter VCO uses an on-board 10 MHz TCXO as a reference clock.

#### **Optional External Clock**

While the ATS9626 features low jitter VCO and a 10 MHz TCXO as the source of the timebase system, there may be occasions when digitizing has to be synchronized to an external clock source.

ATS9626 External Clock option provides an SMA input for an external clock signal, which can be a sine wave or 1.6 V digital signal.

Input impedance for the External Clock input is fixed at 50  $\Omega$ . External clock input is always ac-coupled.

There are two types of External Clock supported by ATS9626: Fast External Clock, and 10 MHz Reference Clock.

#### **Fast External Clock**

A new sample is taken by the on-board ADCs for each rising edge of this External Clock signal.

In order to satisfy the clocking requirements of the ADC chips being used, Fast External Clock frequency must always be higher than 50 MHz and lower than 250 MHz.

This is the ideal clocking scheme for OCT applications

#### **10 MHz Reference Clock**

It is possible to generate the sampling clock based on an external 10 MHz reference input. This is useful for RF systems that use a common 10 MHz reference clock.

ATS9626 uses an on-board low-jitter VCO to generate the 250 MHz high frequency clock used by the ADC. This 250 MS/s sampled data can then be decimated by a factor of 1 to 100000.

#### **Dummy Clock Switchover**

OCT applications require interfacing the ATS9626 to a variable clock frequency (called k-clock) from a swept-source laser.

In most cases, k-clock frequency can be out of specification for a short period of time, i.e. the frequency is slower than 50 MHz for a short period of time.

ATS9626 has a built-in Dummy Clock generator and a clock switchover mechanism that can be used to avoid operating the A/D chips outside of their specifications.

This unique feature of the ATS9626 can be the difference between a fully working OCT system and one that cannot provide reliable data.

#### **AUX Connectors**

ATS9626 provides two AUX (Auxiliary) SMA connectors that can be used for interfacing to external digital signals.

AUX 1 can be configured as either an Input or Output. It is configured as a Trigger Output by default.

AUX 2 is a Trigger Output.

When configured as a Trigger Output, AUX SMA connector outputs a 5 Volt TTL signal synchronous to the ATS9626 Trigger signal, allowing users to synchronize their test systems to the ATS9626 Trigger.

When combined with the Trigger Delay feature of the ATS9626, this option is ideal for ultrasonic and other pulse-echo imaging applications.

AUX connector can also be used as a Trigger Enable Input and Clock Output.

Another application for AUX connector is that users can input the 1 PPS pulse from a GPS receiver into the ATS9626 (and the Coprocessor FPGA).

### **Calibration**

Every ATS9626 digitizer is factory calibrated to NISTor CNRC-traceable standards. To recalibrate an ATS9626, the digitizer must either be shipped back to the factory or a qualified metrology lab.

#### **AlazarDSO Software**

ATS9626 is supplied with the powerful AlazarDSO software that allows the user to setup the acquisition hardware and capture, display and archive the signals.

The Stream-To-Memory command in AlazarDSO allows users to stream a large dataset to motherboard memory.

AlazarDSO software also includes powerful tools for benchmarking the computer bus and disk drive.

#### **Software Development Kits**

AlazarTech provides easy to use software development kits for customers who want to integrate the ATS9626 into their own software.

A Windows and Linux compatible software development kit, ATS-SDK, allows programs written in C/C++, C#, Python, MATLAB, and LabVIEW to fully control the

ATS9626. Sample programs are provided as source code.

The purchase of an ATS-SDK license includes a subscription that provides the following benefits for a period of 12 months from the date of purchase:

- Download ATS-SDK updates from the AlazarTech website;

- Receive technical support on ATS-SDK.

Customers who want to receive technical support and download new releases beyond this 12 month period should purchase extended support and maintenance (order number ATS-SDK-1YR).

#### **ATS-GPU**

ATS-GPU is a software library developed by AlazarTech to allow users to do real-time data transfer from ATS9626 to a GPU card at rates up to 1.6 GB/s.

Modern GPUs include very powerful processing units and a very high speed graphical memory bus. This combination makes them perfectly suited for signal processing applications.

ATS-GPU-BASE is supplied with an example user application in source code. The application includes GPU kernels that use ATS-GPU to receive data, do very simple signal processing (data inversion), and copy the processed (inverted) data back to a user buffer. All this is done at the highest possible data transfer rate.

Programmers can replace the data inversion code with application-specific signal processing kernels to develop custom applications.

ATS-GPU-OCT is the optional OCT Signal Processing library for ATS-GPU. It contains floating point FFT routines that have also been optimized to provide the maximum number of FFTs per second. Kernel code running on the GPU can do zero-padding, apply a windowing function, do a floating point FFT, calculate the amplitude and convert the result to a log scale. It is also possible to output phase information.

FFTs can be done on triggered data or on continuous gapless stream of data. It is also possible to do spectral averaging. Our benchmarks showed that it was possible to do 400,000 FFTs per second when capturing data in single-channel mode and using a NVIDIA GeForce GTX Titan X GPU.

ATS-GPU supports 64-bit Windows and 64-bit Linux for CUDA $^{\rm @}$ -based development.

#### **Support for Windows**

Windows support for ATS9626 includes Windows 7, Windows 8.x, Windows 10, Windows Server 2008 R2, Windows Server 2010 and Windows Server 2013.

Due due to lack of demand and due to the fact that Microsoft no longer supports these operating systems,

AlazarTech no longer supports Windows XP, Windows Vista, and Windows Server 2008.

#### **Linux Support**

AlazarTech offers ATS9626 binary drivers for most of the popular Linux distributions, such as CentOS, Ubuntu,...

Users can download the binary driver for their specific distribution by choosing from the available drivers here:

#### ftp://release@ftp.alazartech.com/outgoing/linux

Also provided is a GUI application called AlazarFront-Panel that allows simple data acquisition and display.

ATS-SDK includes source code example programs for Linux, which demonstrate how to acquire data programmatically using a C compiler.

If customers want to use ATS9626 in any Linux distribution other than the one listed above, they can have the AlazarTech engineering team generate an appropriate driver for a nominal fee.

Based on a minimum annual business commitment, the Linux driver source code license (order number ATS9626-LINUX) may be granted to qualified OEM customers for a fee. For release of driver source code, a Non-Disclosure Agreement must be executed between the customer's organization and AlazarTech.

All such source code disclosures are made on an as-is basis with limited support from the factory.

#### **Export Control Classification**

According to the latest Export Control Handbook that came into effect on August 11, 2017, ATS9626 is classified by Export Controls Division of Government of Canada as a controlled product under ECL 1-3.A.2.h, which is equivalent to ECCN 3A002.h.

For sales where the ultimate country destination is Canada or U.S., no export permit is required unless the end-use of ATS9626, in part or in its entirety, is related to the development or deployment of weapons of mass destruction.

For shipments to <u>eligible destinations</u>, AlazarTech is allowed to export under a general export permit, unless the end-use of ATS9626, in part or in its entirety, is related to the development or deployment of weapons of mass destruction. For general export permit shipments, users must provide a signed export compliance statement (ECS) that includes a detailed description of the end-use. Shipments cannot be made without a signed ECS on file.

For all other countries, and for all cases where the end-use of ATS9626, in part or in its entirety, is related to the development or deployment of weapons of mass destruction, an export permit is required, which will require extensive details on the end-use and end-users. This process may cause significant delays.

#### **RoHS Compliance**

ATS9626 is fully RoHS compliant, as defined by Directive 2015/863/EU (RoHS 3) of the European Parliament and of the Council of 31 March 2015 on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

All manufacturing is done using RoHS-compliant components and lead-free soldering.

#### **EC Conformity**

ATS9626 conforms to the following standards:

Electromagnetic Emissions:

CISPR 22:2006/EN 55022:2006 (Class A):

Information Technology Equipment (ITE). Radio disturbance characteristics. Limits and method of measurement.

Electromagnetic Immunity:

CISPR 24:1997/EN 55024:1998 (+A1 +A2):

Information Technology Equipment Immunity characteristics — Limits and methods of measurement.

#### Safety:

IEC 60950-1:2005: Information technology equipment — Safety — Part 1: General requirements.

IEC 60950-1:2006: Information technology equipment — Safety — Part 1: General requirements.

ATS9626 also follows the provisions of the following directives: 2006/95/EC (Low Voltage Equipment); 2004/108/EC (Electromagnetic Compatibility).

#### FCC & ICES-003 Compliance

ATS9626 has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15, subpart B of the FCC Rules, and the Canadian Interference-Causing Equipment Standard ICES-003:2004.

#### **Processing Using Multiple CPU Cores**

Programmers can take advantage of multiple cores available in modern CPUs to speed up signal processing.

Benchmarks have shown that a quad-core CPU can perform real-time averaging at a rate of 1.0 GB/s and only use up 20% of CPU cycles. Increasing the number of cores or decreasing the sample rate reduces CPU usage even further.

One of the main applications of using multiple cores to do signal processing is Quantum Computing and Spectroscopy applications, where each record contains partial information about the signal of interest and a large number of records must be accumulated to gather a representative dataset.

#### **System Requirements**

Personal computer with at least one free x8 or x16 PCI Express (v1.0a, v1.1 or v2.0) slot, 2 GB RAM, 100 MB of free hard disk space, SVGA display adaptor and monitor with at least a 1024 x 768 resolution.

#### **Power Requirements**

+12 V 2.0 A, typical +3.3 V 2.0 A, typical

**Physical**

Single slot, half length PCI Express Size

card (4.377 inches x 6.5 inches excluding the connectors protruding from the front panel)

Weight

I/O Connectors

ECLK, CH A, CH B, TRIG IN,

AUX I/O 1, AUX I/O 2 SMA female connectors

Environmental

Operating temperature 0 to 55 degrees Celsius Storage temperature -20 to 70 degrees Celsius Relative humidity 5 to 95%, non-condensing

**Acquisition System**

Resolution 16 bits

Bandwidth (-3 dB)

DC-coupled, 50  $\Omega$ Without ATS9626-014 upgrade:

DC - 120 MHz

With ATS9626-014 upgrade:

DC - 100 MHz

Number of channels 2, simultaneously sampled

Maximum Sample Rate 250 MS/s single shot

Minimum Sample Rate 1 KS/s single shot for internal

clocking

Full Scale Input range: ±1.25 V standard. Can be

permanently changed to  $\pm 200 \text{ mV}$ with ATS9626-014 upgrade

Input coupling DC only Input impedance  $50.0 \pm 1\%$

Input protection ±4 V (DC + peak AC for CH A,

> CH B and EXT only without external attenuation)

**Acquisition Memory System**

Memory size 2 GigaSamples

Record length Software selectable with 32-point

resolution. Record length must be a minimum of 256 points. There is no upper limit on the maximum

record length.

Software selectable from a Number of records

> minimum of 1 to a maximum of infinite number of records

Pre-trigger depth From 0 to 4080 for single channel

in NPT mode

From 0 to 2040 for dual channel

in NPT mode

Post-trigger depth Record Length - Pre-Trigger Depth **Timebase System**

Timebase options Internal Clock or

External Clock (Optional)

Internal Sample Rates 250 MS/s, 125 MS/s, 100 MS/s,

50 MS/s, 20 MS/s, 10 MS/s, 5 MS/s, 2 MS/s, 1 MS/s, 500 KS/s, 200 KS/s, 100 KS/s, 50 KS/s, 20 KS/s, 10 KS/s,

5 KS/s, 2 KS/s, 1 KS/s

Internal Clock accuracy ±2 ppm

**Dynamic Parameters**

Typical values measured on CH A of a randomly selected ATS9626. Input signal was provided by a Marconi 2018A signal generator, followed by multi-pole band-pass filters (TTE Q36T family). Inputs were not averaged.

|       | 5 MHz     | 10 MHz    | 20 MHz    | 50 MHz    | 100 MHz   |

|-------|-----------|-----------|-----------|-----------|-----------|

| SNR   | 72.90 dB  | 72.32 dB  | 72.27 dB  | 71.19 dB  | 67.97 dB  |

| SINAD | 72.35 dB  | 71.97 dB  | 71.66 dB  | 65.95 dB  | 58.74 dB  |

| SFDR  | 95.36 dB  | 95.10 dB  | 91.69 dB  | 90.20 dB  | 89.23 dB  |

| THD   | -81.58 dB | -83.06 dB | -80.93 dB | -67.50 dB | -59.28 dB |

| ENOB  | 11.73     | 11.66     | 11.62     | 10.66     | 9.46      |

**Optional ECLK (External Clock) Input**

Signal Level 200 mVp-p to 3.3 Vp-p sine wave

or square wave

Input impedance 50 Ω Input coupling AC

250 MHz for Fast External Clock Maximum frequency Minimum frequency 50 MHz for Fast External Clock

Sampling Edge Risina Maximum amplitude 2 V<sub>p-p</sub>

**Dummy Clock Switchover**

Switchover mode Only when Fast External Clock is

selected

Switchover start Upon end of each record

Switchover time Programmable with 5 ns resolution

**Optional 10 MHz Reference PLL Input**

Signal Level 200 mVp-p to 3.3 Vp-p sine wave

or square wave

Input impedance 50 Ω Input Coupling AC coupled Input frequency  $10 \text{ MHz} \pm 0.1 \text{ MHz}$

Maximum frequency 10.1 MHz Minimum frequency 9.9 MHz Sampling Clock Freq. 250 MHz

**Triggering System**

Mode Edge triggering with hysteresis

Comparator Type Digital comparators for internal (CH A, CH B) triggering and

analog comparators for TRIG IN (External) triggering

Number of Trigger Engines

Trigger Engine Combination Engine J, engine K, J OR K,

software selectable

Trigger Engine Source CH A, CH B, EXT, Software or

None, independently software selectable for each of the two

Trigger Engines

Hysteresis ±5% of full scale input, typical

±10% of full scale input range. Trigger sensitivity

This implies that the trigger system may not trigger reliably if the input has an amplitude less than  $\pm 10\%$ of full scale input range selected

±5%, typical, of full scale input

range of the selected trigger

source

Bandwidth 50 MHz

Trigger level accuracy

Trigger Delay Software selectable from 0 to

9,999,999 sampling clock cycles

Software selectable with a 10 µs Trigger Timeout resolution. Maximum settable

value is 3,600 seconds. Can also be disabled to wait indefinitely for

a trigger event

#### TRIG IN (External Trigger) Input

Input type Digital triggering (LVTTL)

$6.4 \text{ k}\Omega \pm 10\%$ Input impedance Coupling DC only

Minimum pulse width 16 nanoseconds

Minimum pulse amplitude 2 Volt

Absolute maximum input -0.7 V to +8 V

#### **Auxiliary I/O (AUX 1)**

Signal direction Input or Output, software

selectable. Trigger Output by

default

Output types: Trigger Output

**Busy Output**

Software controlled Digital Output

Input types: Trigger Enable

Software readable Digital Input

Output

Amplitude: 5 Volt TTL

Synchronization: Synchronized to a clock derived

from the ADC sampling clock. Divide-by-4 clock (dual channel mode) or divide-by-8 clock

(single channel mode)

Input

Amplitude: 3.3 Volt TTL (5 Volt compliant)

#### **TRIG OUT Output (AUX 2)**

Connector Used AUX I/O Output Signal 5 Volt TTL

Synchronization Synchronized to a clock derived

from the ADC sampling clock. Divide-by-4 clock (dual channel mode) or divide-by-8 clock (single channel mode)

#### **Materials Supplied**

ATS9626 PCI Express Card

ATS9626 Installation Disk (on USB Flash Drive)

#### **Certification and Compliances**

RoHS 3 (Directive 2015/863/EU) Compliance

CE Marking — EC Conformity

FCC Part 15 Class A / ICES-003 Class A Compliance

All specifications are subject to change without notice

#### ORDERING INFORMATION

ATS9626-2G-SL50 ATS9626-002 ATS9626-2G-SE260 ATS9626-003 SyncBoard-9626 2x ATS9626-007 SyncBoard-9626 4x ATS9626-008 ATS9626: ±200mV Input Range Upgrade ATS9626-014 SyncBoard-9626 2x-W ATS9626-020 ATS9626-021 SyncBoard-9626 3x-W SyncBoard-9626 4x-W ATS9626-022 ATS9626-SL50: One Year Extended Warranty ATS9626-061 ATS9626-SE260: One Year Extended Warranty ATS9626-062 Software Development Kit ATS-SDK 1 Year Subscription (Supports C/C++, Python, MATLAB, and LabVIEW)

ATS-GPU-BASE: GPU Streaming Library ATSGPU-001

1 Year Subscription

ATS-GPU-OCT: Signal Processing Library 1 Year Subscription (requires ATSGPU-001)

ATSGPU-101

† AlazarDSO, AlazarTech, and AlazarTech ATS are registered trademarks of Alazar Technologies Inc.

MATLAB is a trademark and/or registered trademark of The MathWorks, Inc. LabVIEW is a trademark and/or registered trademark of National Instruments. Windows and Windows Server are trademarks and/or registered trademarks

of Microsoft Corporation in the U.S. and/or other countries. Linux is a registered trademark of Linus Torvalds.

CUDA is a trademark and/or registered trademark of NVIDIA Corporation

in the U.S. and/or other countries.

Radeon is a trademark of Advanced Micro Devices, Inc.

OpenCL is a trademark of Apple Inc.

All other trademarks are the property of their respective owners.

#### Manufactured By:

#### Alazar Technologies, Inc.

6600 TRANS-CANADA HIGHWAY, SUITE 310 POINTE-CLAIRE, QC, CANADA H9R 4S2

TOLL FREE: 1-877-7-ALAZAR OR 1-877-725-2927 TEL: (514) 426-4899 FAX: (514) 426-2723

F-MAIL: sales@alazartech.com

## **DATASHEET REVISION HISTORY**

| DATASHEET REVISION HISTORY                                                                                                                                                                                                   |                                       |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|

| Changes from version 1.3D (Sept 2018) to version 1.3E                                                                                                                                                                        | Section,                              | Page   |

| Removed references to the user-programmable FPGA and related FPGA Devel as the FPGA Development Kit is being discontinued                                                                                                    | opment Kit Global o                   | change |

| Updated block diagram to indicate Coprocessor FPGA model for each ATS9626                                                                                                                                                    | 5 model Block diagram,                | pg. 2  |

| Updated <i>Optional High Capacity Coprocessor FPGA</i> section: larger Coprocess FPGA is no longer available as an upgrade, users must order ATS9626-2G-S in order to have the high-capacity P3SE260H780C4N Coprocessor FPGA |                                       | pg. 3  |

| Removed ATS-GMA section as this product is being discontinued                                                                                                                                                                | ATS-GMA,                              | pg. 7  |

| Specified that listed Pre-trigger depth applies to NPT mode                                                                                                                                                                  | On-Board Acquisition Memory System,   | pg. 9  |

| Removed ATS9626-FDK, ATSGMA-001, ATSGMA-101                                                                                                                                                                                  | Ordering Information,                 | pg. 10 |

| Added Windows Server to Trademark information                                                                                                                                                                                |                                       | pg. 10 |

| Changes from version 1.3C (Jan 2018) to version 1.3D                                                                                                                                                                         | Section,                              | Page   |

| Updated RoHS Compliance to RoHS 3                                                                                                                                                                                            | Global o                              | change |

| Updated product image                                                                                                                                                                                                        |                                       | pg. 1  |

| Clarified Operating System Support                                                                                                                                                                                           | Feature Table,                        | pg. 1  |

| Added AUX connector configurations for AUX 1 and AUX 2                                                                                                                                                                       | AUX Connectors,                       | pg. 6  |

| Added information on ATS-SDK license                                                                                                                                                                                         | Software Development Kits,            | pg. 6  |

| Specified 64-bit version for Windows and Linux support                                                                                                                                                                       | ATS-GPU,                              | pg. 7  |

| Added ATS-GMA section                                                                                                                                                                                                        | ATS-GMA,                              | pg. 7  |

| Added list of supported Microsoft Windows versions                                                                                                                                                                           | Support for Windows,                  | pg. 7  |

| Added Acquisition Memory System section                                                                                                                                                                                      | Acquisition Memory System,            | pg. 9  |

| Added Maximum Amplitude: 2 V <sub>D-D</sub>                                                                                                                                                                                  | Optional ECLK (External Clock) Input, | pg. 9  |

| Added "PLL" to section name for clarity, corrected Input Frequency tolerance, and added Max. and Min. Frequencies                                                                                                            | Optional 10 MHz Reference PLL Input,  | pg. 9  |

| Corrected Trigger Engine Combination                                                                                                                                                                                         | Triggering System,                    | pg. 9  |

| Added Auxiliary I/O (AUX 1) section                                                                                                                                                                                          | Auxiliary I/O (AUX 1),                | pg. 10 |

| Edited TRIG OUT Output section title to include (AUX 2)                                                                                                                                                                      | TRIG OUT Output (AUX 2),              | pg. 10 |

| Added subscription length for ATS-SDK, ATSGPU-001, ATSGPU-101<br>Added products ATSGMA-001, ATSGMA-101                                                                                                                       | Ordering Information,                 | pg. 10 |

| Added Trademark information                                                                                                                                                                                                  |                                       | pg. 10 |

| Changes from version 1.3B (Oct 2017) to version 1.3C                                                                                                                                                                         | Section,                              | Page   |

| Added note about NPT Footers                                                                                                                                                                                                 | No Pre-Trigger (NPT) AutoDMA,         | pg. 4  |

| Added CNRC as calibration standard                                                                                                                                                                                           | Calibration,                          | pg. 6  |

| Added -BASE and -OCT to ATS-GPU description for clarity                                                                                                                                                                      | ATS-GPU,                              | pg. 6  |

| Corrected size of card                                                                                                                                                                                                       | Physical,                             | pg. 9  |

| Updated email address                                                                                                                                                                                                        | Manufactured By,                      | pg. 10 |

| Changes from version 1.3A (Sept 2017) to version 1.3B                                                                                                                                                                        | Section,                              | Page   |

| Updated description for product ATSGPU-001 & ATSGPU-101                                                                                                                                                                      | Ordering Information System,          | _      |

| Changes from version 1.3 (Mar 2017) to version 1.3A                                                                                                                                                                          | Section                               | Page   |

|                                                                                                                                                                                                                              | Section,                              | _      |

| Added section on External Trigger Input                                                                                                                                                                                      | External Trigger Input,               |        |

| Modified AlazarDSO description                                                                                                                                                                                               | AlazarDSO Software,                   |        |

| Specified conditions for obtaining a Linux driver source code license                                                                                                                                                        | Linux Support,                        |        |

| Replaced ATS-GPU Compatibility section with new ATS-GPU section                                                                                                                                                              | ATS-GPU,                              |        |

| Replaced section ATS-Linux with Linux Support; now includes download link                                                                                                                                                    |                                       |        |

| Added Export Control Classification information                                                                                                                                                                              | Export Control Classification,        |        |

| Added section on RoHS compliance                                                                                                                                                                                             | RoHS Compliance,                      | ρg. /  |

## **DATASHEET REVISION HISTORY**

| Changes from version 1.3 (Mar 2017) to version 1.3A (contin         | ued) Section, Page                       |

|---------------------------------------------------------------------|------------------------------------------|

| Added section on EC Conformity                                      | EC Conformity, pg. 7                     |

| Added section on FCC & ICES-003 Compliance                          | FCC & ICES-003 Compliance, pg. 7         |

| Updated External Trigger Input Impedance to 6.4 k $\Omega$ ±10%     | TRIG IN (External Trigger) Input, pg. 10 |

| Updated list of Certification and Compliances                       | Certification and Compliances, pg. 10    |

| Removed products ATS9626-LINUX, ATSGPU-BASE, ATSGPU-ANN, ATSGPU-FFT | Ordering Information System, pg. 10      |

| Added products ATS9626-061, ATS9626-062, ATSGPU-001, ATSGPU-101     | Ordering Information System, pg. 10      |

| Corrected product name for ATS-SDK                                  | Ordering Information, pg. 10             |

| Changes from version 1.1C (Jan 2013) to version 1.3                               | Section, Page                    |

|-----------------------------------------------------------------------------------|----------------------------------|

| Added Python to list of supported SDK programming languages                       | Features + Overview, pg. 1       |

| Updated list of supported Operating Systems                                       | Feature Table, pg. 1             |

| Corrected ATS9626 Coprocessor FPGA Development Kit name & part number             | Overview, pg. 1                  |

| Modified SDK description to add Python support and remove ATS-VI                  | Overview, pg. 1                  |

| Added analog input bandwidth specifications specific to ATS9626-014 upgrade       | Analog Input, pg. 2              |

| Added 2-slot-spacing SyncBoards (-W models)                                       | Master/Slave Systems, pg. 5      |

| Modified SDK description to add Python support and remove ATS-VI                  | Software Development Kits, pg. 6 |

| Replaced GPU Based Signal Processing information with ATS-GPU Compatibility       | ATS-GPU Compatibility, pg. 6     |

| Added acquisition system bandwidth specifications specific to ATS9626-014 upgrade | Acquisition System, pg. 8        |

| Added new part numbers to Ordering Information                                    | Ordering Information, pg. 9      |